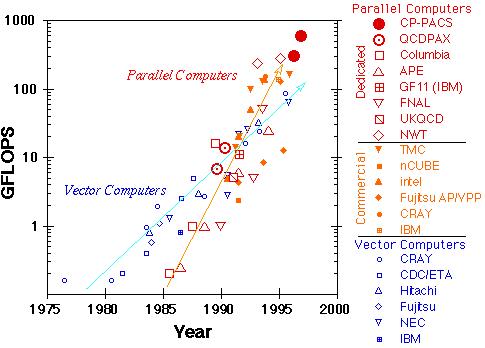

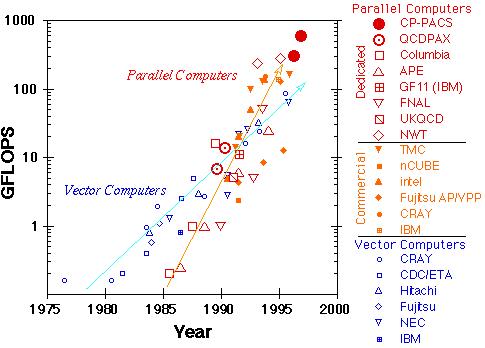

Development of Parallel Computer and CP-PACS

October 1996

CP-PACS computer

| Theoretical peak speed |

| ||||||||||

| Total main memory |

| ||||||||||

| Node processor | Architecture |

| |||||||||

| Floating point registers | 128(64bit) physical registers | ||||||||||

| Clock cycle | 150MHz | ||||||||||

| Cache memory size |

| ||||||||||

| Network | Topology |

| |||||||||

| Data transfer throughput | 300MByte/sec (per link) | ||||||||||

| Method | wormhole +remote DMA | ||||||||||

| Disk system | 529GByte(distributed RAID-5 disk) | ||||||||||

| External connection | HIPPI | Theoretical peak throughput 100Mbyte/sec | |||||||||

| Ethernet | Theoretical peak throughput 1.2Mbyte/sec | ||||||||||

| Size | 7.0m(width)x4.2m(depth)x2.0m(height) | ||||||||||

| Power dissipation | 275 kW maximum | ||||||||||

Further details

Development of Parallel Computer and CP-PACS

October 1996