PAX-32 has 32 PU(processing unit) connected in 8 x 4 two-dimensional torus.

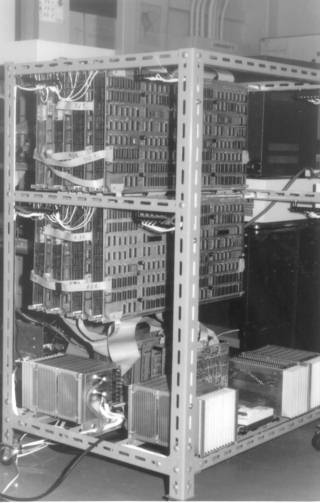

PU array is folded to install in compact size as shown in the Photo(right).

PAX-32 has 32 PU(processing unit) connected in 8 x 4 two-dimensional torus.

PU array is folded to install in compact size as shown in the Photo(right).

A processing unit has an 8-bit microprocessor(M6800),

a floating point unit(AM9511) and 12KBytes of memory.

Processing unit of PAX-32 [300KB]

PU array of PAX-32 is connected to a Control unit, and

the Control unit is connected to a Host computer.

System configuration of PAX-32 and PAX-128 [44KB]

A language SPL/M for PAX-32 and its compiler was developped at Kyoto University by Sato. The compiler runs on the Host computer, and the object code is loaded to each PU through the Control unit.

Peak performance of PAX-32 was 0.5 Mflops on solving Poissson equation.

PAX-32 was made in 1980 by

Prof.T.Hoshino and the members of his laboratory

at Kyoto University .

The name of this system, once had been PACS-32 standing for

"Processor Array for Continuum Simulation", was changed to PAX-32

standing for "Processor Array eXperiment" after it was moved to Tsukuba.

* flops : float(single precision) operations per second peak performance.