CP-PACSのCPUチップは0.3ミクロンCMOS半導体技術により作成され、サイズは 15.7mm x 15.7mm である。チップのレイアウトを下図に示す。 PVP-SW機構は、 左上の部分に浮動小数点演算ユニットと並んで実装された128個の浮動小数点 レジスタを用いて実現されている。

CPUチップは、サイズ5.7cm x 5.7cmのセラミックマルチチップモジュール中央

部に搭載される(下図)。このモジュール上に、左上から順に、

CPU、ストレージコントローラ

(SC)、そしてネットワークアダプタ(NIA)が一列に配置されている。SCとNIA

は0.5ミクロンゲートアレイ技術により製作されている。周囲を占める12個の金

色のチップは二次キャッシュメモリである。

CP-PACS processor module

CP-PACSのボードは45.6cm x 62.5cmのサイズを持ち、8個のPUモジュールとそれぞれの DRAMを搭載する。下図のボード8分割それぞれの中央部分が放熱フィンの付けられたPU モジュールであり、上下の白色部分は、DRAMと主記憶間のメモリコントロールユニット である。黒い部分は4Mbit DRAMを搭載するDIMモジュールであり、各PUあたり 64MByteが実装されている。以上の他、各ボードはx方向のクロスバーチップ二個と クロック分配用チップ一個を搭載する。

CP-PACS board

PU用の一筐体は、16枚のPUボードと1枚のIOUボードを上下二段、計34枚格納する。

y方向クロスバーは各PU筐体のボード搭載用バックプレーンに実装される。

z方向クロスバーは専用ボードにまとめて実装され、別筐体に格納される。

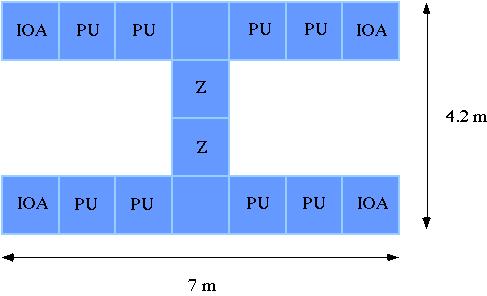

CP-PACSの筐体配置を下図に示す。PUの記号は、PUボードとIOUボードを格納

する筐体を示し、Zの記号の筐体はZクロスバーのためのものである。

IOAにはI/Oアダプタが搭載されている。

RAID-5規格の分散磁気ディスクは、CP-PACS本体から数m離れて設置され、IOAを通じて

IOUとSCSI-IIバスで接続されている。

CP-PACS全体の冷却は、床下からの強制空冷である。

CP-PACSの筐体配置