## Development of Parallel Computers at Tsukuba from PACS-9 (1978) to PACS-CS (2006)

## PACS/PAX Computers (1978-1989)

University of Tsukuba is one of the pioneering institutes in the development of parallel computers in Japan. In 1977, Tsutomu Hoshino and Toshio Kawai started to construct parallel computers at Tsukuba, adopting two-dimensional torus network as the fundamental architecture. The first computer "PACS-9" was constructed in 1978 and achieved the speed of 7000 operations/sec. Since then, a series of parallel computers have been developed and applied for simulations of physical systems such as the nuclear matter in the reactor.

#PU Performance Machines Memory PACS-9 7 KFLOPS 0.5 MFLOPS 1980 PAX-32 0.5MB 1983 PAX-128 4 MFLOPS 128 5 MB 1984 PAX-32J 3 MFLOPS 4 MB 1989 QCDPAX 14 GFLOPS 480 3 GB 1996 CP-PACS 2048 614 GFLOPS 128 GB 2006 PACS-CS 2560 14 TFLOPS 5 TB

PACS-9 (1978)

PAX-32 (1980)

History of PACS/PAX computers

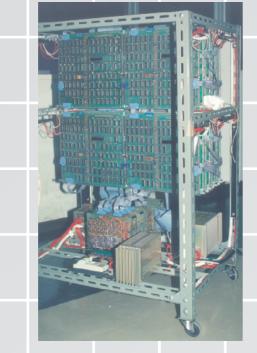

QCDPAX (1989)

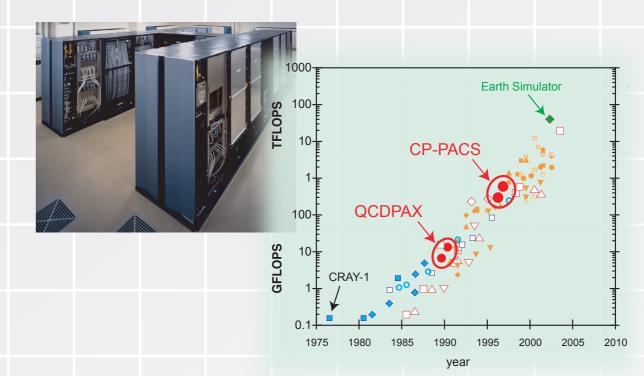

QCDPAX, developed in 1989 as the fifth computer of the series, is dedicated for the simulation of Quamtum Chromodynamics, the fundamental theory of quarks. QCDPAX consists of 480 processing units. With the peak speed of 14 GFLOPS, QCDPAX carried out simulations of quarks at zero and finite temperatures.

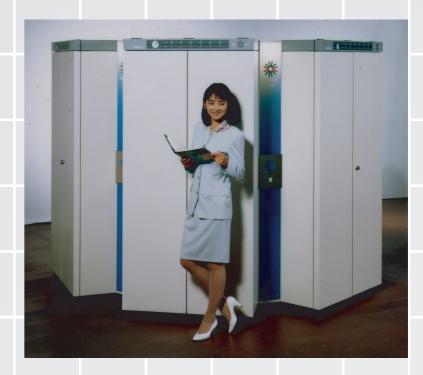

## CP-PACS (1996-2005)

CP-PACS is the sixth of the PACS/PAX parallel computers. With 2048 processing units and 128 I/O nodes interconnected by a three-dimensional Hyper-Crossbar network, CP-PACS achieved the peak speed of 614 GFLOPS and was ranked No.1 in the TOP 500 list for supercomputers in November 1996. CP-PACS has been intensively applied for simulations in the Physics of Fields ranging from quarks to the universe. CP-PACS was shut down in September 2005.

Development of high performance computers

## PACS-CS (2006)

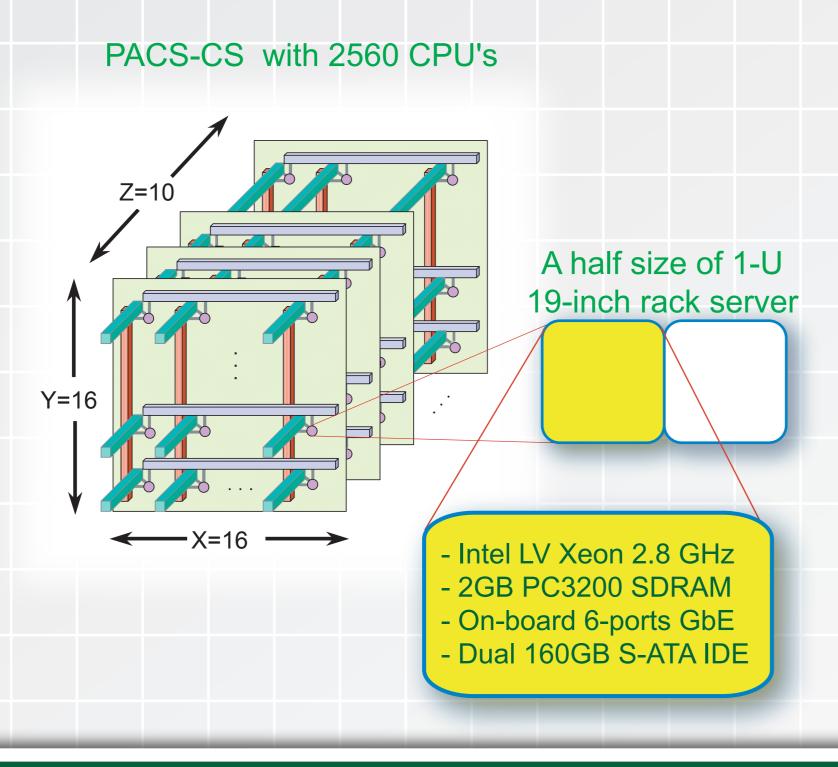

PACS-CS is the seventh generation of the PACS series, a PC-cluster with 2560 CPUs and 14.3 TFLOPS of peak performance. The building block is a specially designed 1-U size board which contains two sets of separated Linux-ready PC without SMP configuration. Since each CPU on the board accesses memory and network interface with full bandwidth, the potential performance is significantly higher than standard dual-CPU SMP servers, albeit keeping the same density. PACS-CS is also equipped with a specially designed 3-D Hyper-Crossbar Network based on channel-bonding technology of Gigabit Ethernet to provide high bisection bandwidth with low cost. PACS-CS started operation in July 2006.