# SCIMAS Software Controlled Integrated Memory Architecture for HPG

### **Background**

- Memory wall problem

- Conventional Cache is not good in HPC

- unwilling line conflict

- fixed size of Off-Chip Memory access

## Solution: SCIMA (Software Controlled Integrated Memory Architecture)

- Strategy: software controllability

- Addressable On-Chip Memory in addition to conventional cache

- On-Chip Memory and cache are reconfigurable

- Explicit data transfer between On-Chip Memory and Off-Chip Memory by page-load/page-store instruction

- burst transfer and stride transfer are supported

#### advantages of SCIMA

Tb: CPU busy time

Ti: Latency stall time

Tt: Throughput stall time

| On-Chip Memory Features                | $T_b$    | Tı       | $T_t$    |

|----------------------------------------|----------|----------|----------|

| software controllability               | -        | -        | <b>1</b> |

| page-load/page-store(burst)            | <b>†</b> | <b>1</b> | -        |

| page-load/page-store(stride)           | 1        | <b>1</b> | <b>1</b> |

| scheduling for page-load/page-store    | -        | <b>+</b> | -        |

| Latency Tolerating Techniques of Cache | $T_b$    | Ti       | $T_t$    |

| larger cache line                      | -        | <b>1</b> | 1        |

| lock-up free cache                     | -        | <b>1</b> | 1        |

| cache prefetching                      | <b>†</b> | 1        | 1        |

#### **Schematic View**

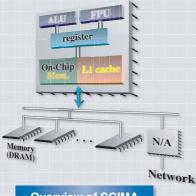

Overview of SCIMA

**Address Space**